| Title              | Reference Design Report for a 5 W Charger Using LNK616PG |  |  |  |

|--------------------|----------------------------------------------------------|--|--|--|

| Specification      | 85-265 VAC Input; 5 V, 1 A Output                        |  |  |  |

| Application        | Low-cost Charger or Adapter                              |  |  |  |

| Author             | Applications Engineering Department                      |  |  |  |

| Document<br>Number | RDR-158                                                  |  |  |  |

| Date               | November 25, 2008                                        |  |  |  |

| Revision           | 1.1                                                      |  |  |  |

#### **Summary and Features**

- Revolutionary control concept provides very low cost, low part-count solution

- Primary-side control eliminates secondary-side control and optocoupler

- Provides  $\pm 5\%$  constant voltage (CV) and  $\pm 10\%$  constant current (CC) accuracy including output cable drop compensation for 26 AWG (0.49  $\Omega$ ) or 24 AWG (0.3  $\Omega$ ) cables

- Over-temperature protection tight tolerance (±5%) with hysteretic recovery for safe PCB temperatures under all conditions

- Auto-restart output short circuit and open-loop protection

- Extended pin creepage distance for reliable operation in humid environments –

>3.2 mm at package

- EcoSmart® Easily meets all current international energy efficiency standards China (CECP) / CEC / ENERGY STAR 2 / EU CoC

- No-load consumption <50 mW at 230 VAC</li>

- Ultra-low leakage current: <5 µA at 265 VAC input (no Y capacitor required)</li>

- Design easily passes EN550022 and CISPR-22 Class B EMI testing with >10 dB margin

- Meets IEC 61000-4-5 Class 3 AC line surge

- Meets IEC 61000-4-2 ESD withstand (contact and air discharge to ±15 kV)

#### PATENT INFORMATION

The products and applications illustrated herein (including transformer construction and circuits external to the products) may be covered by one or more U.S. and foreign patents, or potentially by pending U.S. and foreign patent applications assigned to Power Integrations. A complete list of Power Integrations' patents may be found at www.powerint.com. Power Integrations grants its customers a license under certain patent rights as set forth at <a href="http://www.powerint.com/ip.htm">http://www.powerint.com/ip.htm</a>.

| Table of Contents                                                |          |

|------------------------------------------------------------------|----------|

| 1 Introduction                                                   | 4        |

| 2 Power Supply Specification                                     | 6        |

| 3 Schematic                                                      |          |

| 4 Circuit Description                                            | 8        |

| 4.1 Input Filter                                                 | 8        |

| 4.2 LNK616PG Primary                                             |          |

| 4.3 Output Rectification and Filtering                           | 8        |

| 4.4 Output Regulation                                            |          |

| 5 PCB Layout                                                     | 10       |

| 6 Bill of Materials                                              | 11       |

| 7 Transformer Specification                                      | 12       |

| 7.1 Electrical Diagram                                           | 12       |

| 7.2 Electrical Specifications                                    | 12       |

| 7.3 Materials                                                    | 13       |

| 7.4 Transformer Build Diagram                                    | 13       |

| 7.5 Transformer Construction                                     |          |

| 8 Design Spreadsheet                                             | 15       |

| 9 Performance Data                                               | 18       |

| 9.1 Efficiency                                                   | 18       |

| 9.2 Active Mode CEC Measurement Data                             | 19       |

| 9.2.1 Energy Star v1.1 / CEC (2008)                              |          |

| 9.2.2 Energy Star v2 (April 2008)                                | 20       |

| 9.3 No-Load Input Power                                          | 21       |

| 9.4 Regulation                                                   |          |

| 9.4.1 Load, Line and Temperature                                 | 22       |

| 10 Thermal Performance                                           |          |

| 10.1 Operating Temperature Survey                                |          |

| 11 Waveforms                                                     |          |

| 11.1 Drain Voltage and Current, Normal Operation                 |          |

| 11.2 Output Voltage Start-up Profile                             |          |

| 11.2.1 No-Load Output Voltage Start-up Characteristic            |          |

| 11.2.2 Output Voltage Start-up Characteristic - Resistive Load ( | 5 Ω)28   |

| 11.2.3 Output Voltage Start-up Characteristic - Battery-simulato | r Load29 |

| 11.3 Drain Voltage and Current Start-up Profile                  | 30       |

| 11.4 Load Transient Response (50% to 100% Load Step)             | 31       |

| 11.5 Output Ripple Measurements                                  | 32       |

| 11.5.1 Ripple Measurement Technique                              |          |

| 11.5.2 Ripple Measurement Results                                | 33       |

| 12 Line Surge                                                    |          |

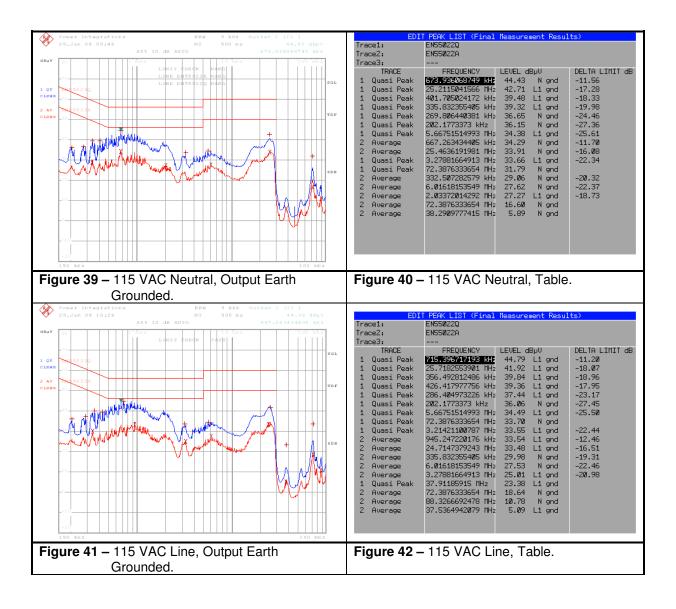

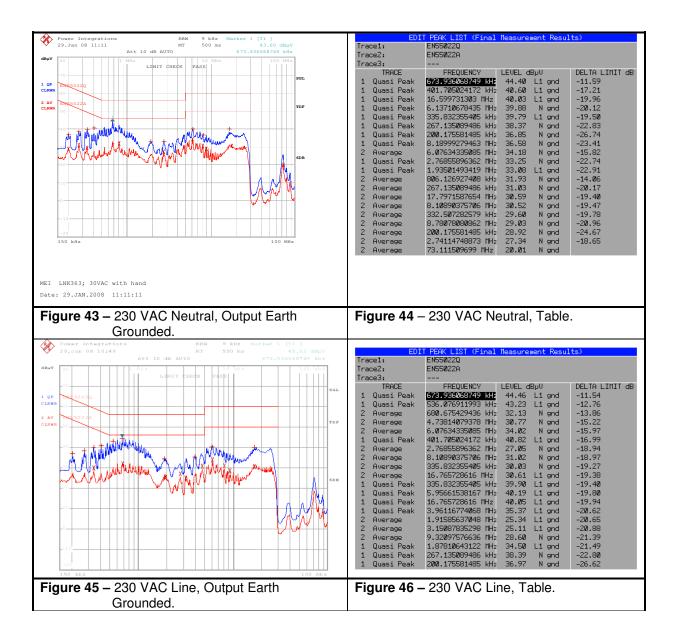

| 13 Conducted EMI                                                 | 36       |

| 14 Revision History                                              | 38       |

# **Important Note:**

Although this board is designed to satisfy safety isolation requirements, the engineering prototype has not been agency approved. Therefore, all testing should be performed using an isolation transformer to provide the AC input to the prototype board.

### 1 Introduction

This engineering report describes a 5 W constant voltage/constant current (CV/CC) universal-input power supply for cell phone or similar charger applications. This reference design is based on the LinkSwitch-II family product LNK616PG.

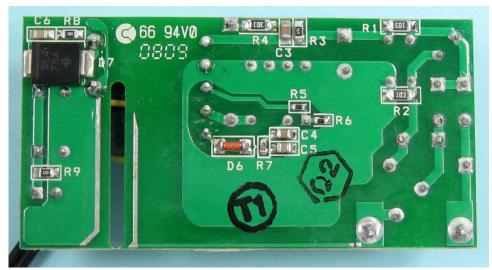

Figure 1 – RD-158 Board Photograph (top and bottom views).

The LNK616PG was developed to cost effectively replace all existing solutions in low-power charger and adapter applications. Its core controller is optimized for CV/CC charging applications with minimal external parts count and very tight control of both the output voltage and current, without the use of an optocoupler. The LNK616PG has an integrated 700 V switching MOSFET and ON/OFF control function which together deliver high efficiency under all load conditions and low no-load energy consumption. Both the operating efficiency and no-load performance exceed all current international energy efficiency standards.

The LNK616PG monolithically integrates the 700 V power MOSFET switch and controller. A unique ON/OFF control scheme provides CV regulation. The IC also incorporates both output cable voltage-drop compensation and tight regulation over a wide temperature range for enhanced CV control. The switching frequency is modulated to regulate the output current for a linear CC characteristic.

The LNK616PG controller consists of an oscillator, a feedback (sense and logic) circuit, a 5.8 V regulator, BYPASS pin programming functions, over-temperature protection, frequency jittering, a current-limit circuit, leading-edge blanking, a frequency controller for CC regulation, and an ON/OFF state machine for CV control.

The LNK616PG also provides a sophisticated range of protection features including autorestart for control loop component open/short circuit faults and output short circuit conditions. Accurate hysteretic thermal shutdown ensures safe average PCB temperatures under all conditions.

The IC package provides extended creepage distance between high and low voltage pins (both at the package and PCB), which is required in highly humid environments to prevent arcing and to further improve reliability.

The LNK616PG can be configured to either be self-biased from the high-voltage DRAIN pin, or to receive an optional external bias supply. When configured to be self-biased, the very low IC current consumption ensures a worst-case no-load power consumption of less than 175 mW at 265 VAC, well within the 300 mW European Union CoC limit. When fed from an optional bias supply (as in this design), the no-load power consumption reduces to <50 mW.

The EE16 transformer bobbin in this design provides extended creepage to meet safety spacing requirements.

This document contains the power supply specifications, schematic, bill of materials, transformer specifications, and typical performance characteristics for this reference design.

# 2 Power Supply Specification

| Description                                                                                                              | Symbol                                                                                  | Min         | Тур                                                  | Max                      | Units                   | Comment                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-------------|------------------------------------------------------|--------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------|

| Input Voltage Frequency No-load Input Power                                                                              | V <sub>IN</sub><br>f <sub>LINE</sub><br>P <sub>NL</sub>                                 | 85<br>47    | 50/60                                                | 265<br>64<br>50          | VAC<br>Hz<br>mW         | 2 Wire – no P.E.  Measured at $V_{IN}$ = 230 VAC                                                             |

| Output Output Voltage Output Ripple Voltage Output Current Output Cable Resistance Output Power Name plate output rating | V <sub>OUT</sub> V <sub>RIPPLE</sub> I <sub>OUT</sub> R <sub>CBL</sub> P <sub>OUT</sub> | 4.75<br>900 | 5.00<br>150<br>1000<br>0.3<br>5                      | 5.25<br>1100             | V<br>mV<br>mA<br>Ω<br>W | All measured at end of cable ±5% 20 MHz bandwidth ±10% 6 ft, 24 AWG                                          |

| Name plate Voltage<br>Nameplate Current<br>Nameplate Power                                                               | V <sub>NP</sub><br>I <sub>NP</sub><br>P <sub>NP</sub>                                   |             | 5<br>900<br>4.5                                      |                          | V<br>mA<br>W            |                                                                                                              |

| Efficiency Average Active Mode                                                                                           | η                                                                                       |             | 74                                                   |                          | %                       | 115 VAC / 230 VAC, 25 °C                                                                                     |

| Required average efficiency per<br>Energy Star EPS v1.1 / CEC<br>2008                                                    | η <sub>ESV1.1</sub>                                                                     | 64          | Efficiency of<br>Supplies (Au                        | Single-Vo<br>ugust 11, 2 | ltage Exter<br>2004)".  | Method for Calculating the Energy nal AC-DC and AC-AC Power                                                  |

| Required average efficiency per<br>Energy Star EPS v2 April, 2008                                                        | $\eta_{ESV2}$                                                                           | 67          | η <sub>ESV1</sub> :(0.09<br>η <sub>ESV2</sub> :(0.07 |                          |                         |                                                                                                              |

| Environmental Conducted EMI Safety                                                                                       |                                                                                         |             | SPR22B / EN<br>et IEC950, UI                         |                          | ss II                   | >10 dB margin                                                                                                |

| Line Surge<br>Differential<br>Common Mode                                                                                |                                                                                         | 1<br>2      |                                                      |                          | kV<br>kV                | 1.2/50 $\mu s$ surge, IEC 1000-4-5, Series Impedance: Differential Mode: 2 $\Omega$ Common Mode: 12 $\Omega$ |

| ESD                                                                                                                      |                                                                                         | -15         |                                                      | 15                       | kV                      | Contact and air discharge to IEC 61000-4-2                                                                   |

| Ambient Temperature                                                                                                      | T <sub>AMB</sub>                                                                        | 0           |                                                      | 40                       | °C                      | Case external, free convection, sea level                                                                    |

#### 3 **Schematic**

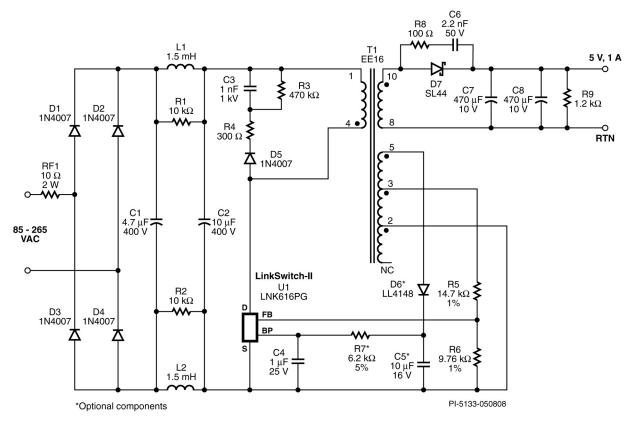

Figure 2 - RD158 Circuit Schematic.

# 4 Circuit Description

This circuit uses the LNK616PG in a primary-side regulated flyback power-supply configuration.

### 4.1 Input Filter

The AC input power is rectified by diodes D1 through D4. The rectified DC is filtered by the bulk storage capacitors C1 and C2. Inductors L1 and L2, with capacitors C1 and C2, form pi  $(\pi)$  filters to attenuate conducted differential-mode EMI noise. This configuration, along with Power Integrations' transformer E-shield technology, allows this design to meet EMI standard EN55022 class B with good margin and without a Y capacitor. The transformer construction also gives very good EMI repeatability. Fusible resistor RF1 provides protection against catastrophic failure. It should be rated to withstand the instantaneous dissipation when the supply is first connected to the AC input (while the input capacitors charge) at VAC<sub>MAX</sub>. This means choosing either an over-sized metal-film or a wire-wound type. This design uses a wire-wound resistor for RF1.

### 4.2 LNK616PG Primary

The LNK616PG device (U1) incorporates the power switching device, oscillator, CV/CC control engine, and startup and protection functions all on one IC. Its integrated 700 V MOSFET allows sufficient voltage margins in universal input AC applications, including extended line swells. The device is self-powered from the BYPASS pin via the decoupling capacitor C4. The value of C4 also programs the cable-drop voltage compensation. In this case, a 1  $\mu F$  capacitor gives the 350 mV (7% of  $V_{NO}$ ) compensation needed for the nominal 24-AWG cable, with 0.3  $\Omega$  impedance, used in this design. The optional bias circuit consisting of D6, C5, and R7 increases efficiency and reduces no-load input power.

The rectified and filtered input voltage is applied to one end of the transformer (T1) primary winding. The other side of the transformer's primary winding is driven by the internal MOSFET of U1. An RCD-R clamp consisting of D5, R3, R4, and C3 limits drainvoltage spikes caused by leakage inductance. Resistor R4 has a relatively large value to prevent any excessive ringing on the drain voltage waveform caused by the leakage inductance. Excessive ringing can increase output ripple by introducing an error in the sampled output voltage. IC U1 samples the feedback winding each cycle, 2.5 µs after turn-off of its internal MOSFET.

# 4.3 Output Rectification and Filtering

Transformer T1's secondary is rectified by D7, a Schottky barrier-type diode (chosen for higher efficiency), and filtered by C7 and C8. In this application, C7 and C8 have sufficiently low ESR characteristics to allow meeting the output voltage ripple requirement without adding an LC post filter. Resistor R8 and capacitor C6 dampen high-frequency ringing and reduce the voltage stress on D7.

In designs where lower average efficiency is acceptable (by 3% to 4%) D7 may be replaced by a PN-junction to lower cost. In this case, ensure R5 and R6 are re-adjusted as necessary to keep the output voltage centered.

## 4.4 Output Regulation

The LNK616PG regulates output using ON/OFF control for CV regulation, and frequency control for CC regulation. The output voltage is sensed by a bias winding on the transformer. The feedback resistors (R5 and R6) were selected using standard 1% resistor values to center both the nominal output voltage and constant current regulation thresholds. Resistor R9 provides a minimum load to maintain output regulation when the output is unloaded.

# 5 PCB Layout

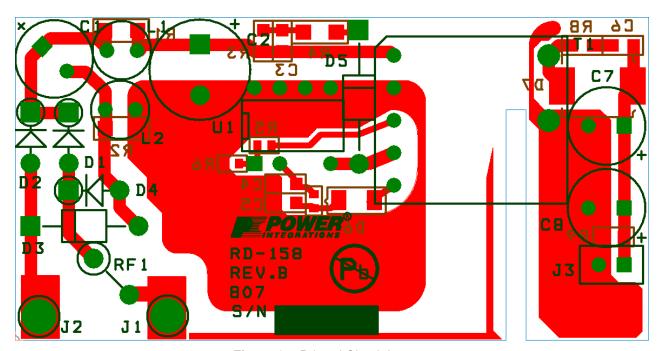

Notable layout design points are:

- A spark gap and associated slot in the PCB between the primary and secondary allows successful ESD testing up to ±15 kV.

- The preferential arcing point routes the energy from ESD discharges back to the AC input, away from the transformer and primary circuitry.

- The trace connected to the AC input side of the spark gap is spaced away from the rest of the board and its components to prevent arc discharges to other sections of the circuit.

- 2 The drain trace length has been minimized to reduce EMI.

- Clamp and output diode loop areas are minimized to reduce EMI.

- The AC input is located away from switching nodes to minimize noise coupling that may bypass input filtering.

- 5 Place C4 (the bypass capacitor) as close as possible to the BYPASS pin on U1.

Figure 3 - Printed Circuit Layout.

# 6 Bill of Materials

|      | _   | Ref                  |                                                                                                  |                                                |                                     |

|------|-----|----------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------------------------|

| Item | Qty | Des                  | Description                                                                                      | Mfg                                            | Mfg Part Number                     |

| 1    | 1   | C1                   | 4.7 μF, 400 V, Electrolytic, (8 x 11.5)                                                          | Taicon<br>Corporation                          | TAQ2G4R7MK0811MLL3                  |

| 2    | 1   | C2                   | 10 $\mu$ F, 400 V, Electrolytic, Low ESR, 79 mA, (10 x 12.5)                                     | Ltec                                           | TYD2GM100G13O                       |

| 3    | 1   | C3                   | 1 nF, 1000 V, Ceramic, X7R, 0805                                                                 | Kemet                                          | C0805C102KDRACTU                    |

| 4    | 1   | C4                   | 1 μF, 25 V, Ceramic, X7R, 0805                                                                   | Panasonic                                      | ECJ-2FB1E105K                       |

| 5    | 1   | C5                   | 10 μF, 16 V, Ceramic, X5R, 0805                                                                  | Murata                                         | GRM21BR61C106KE15L                  |

| 6    | 1   | C6                   | 2.2 nF, 50 V, Ceramic, X7R, 0805                                                                 | Panasonic                                      | ECJ-2VB1H222K                       |

| 7    | 2   | C7 C8                | 470 μF, 10 V, Electrolytic, Very Low ESR, 72 mOhm, (8 x 11.5)                                    | Nippon Chemi-<br>Con                           | EKZE100ELL471MHB5D                  |

| 8    | 5   | D1 D2<br>D3 D4<br>D5 | 1000 V, 1 A, Rectifier, DO-41                                                                    | Vishay                                         | 1N4007-E3/54                        |

| 9    | 1   | D6                   | 75 V, 0.15 A, Fast Switching, 4 ns, MELF                                                         | Diode Inc.                                     | LL4148-13                           |

| 10   | 1   | D7                   | 40 V, 4 A, Schottky, SMD, DO-214AB                                                               | Vishay                                         | SL44-E3/57T                         |

| 11   | 2   | J1 J2                | Test Point, WHT, THRU-HOLE MOUNT                                                                 | Keystone                                       | 5012                                |

| 12   | 1   | J3                   | 6 ft, 24 AWG, 2.1 mm connector (custom)                                                          | CUI Inc                                        | CA-2184                             |

| 13   | 2   | L1 L2                | 1.5 mH, 0.18 A, 5.5 x 10.5 mm                                                                    | Tokin                                          | SBC1-152-181                        |

| 14   | 2   | R1 R2                | 10 kΩ, 5%, 1/4 W, Metal Film, 1206                                                               | Panasonic                                      | ERJ-8GEYJ103V                       |

| 15   | 1   | R3                   | 470 kΩ, 5%, 1/8 W, Metal Film, 0805                                                              | Panasonic                                      | ERJ-6GEYJ474V                       |

| 16   | 1   | R4                   | 300 Ω, 5%, 1/4 W, Metal Film, 1206                                                               | Panasonic                                      | ERJ-8GEYJ301V                       |

| 17   | 1   | R5                   | 14.7 k $\Omega$ , 1%, 1/16 W, Metal Film, 0603                                                   | Panasonic                                      | ERJ-3EKF1472V                       |

| 18   | 1   | R6                   | 9.76 kΩ, 1%, 1/16 W, Metal Film, 0603                                                            | Panasonic                                      | ERJ-3EKF9761V                       |

| 19   | 1   | R7                   | 6.2 kΩ, 5%, 1/10 W, Metal Film, 0603                                                             | Panasonic                                      | ERJ-3GEYJ622V                       |

| 20   | 1   | R8                   | 100 Ω, 5%, 1/8 W, Metal Film, 0805                                                               | Panasonic                                      | ERJ-6GEYJ101V                       |

| 21   | 1   | R9                   | 1.2 kΩ, 5%, 1/8 W, Metal Film, 0805                                                              | Panasonic                                      | ERJ-6GEYJ122V                       |

| 22   | 1   | RF1                  | 10 $\Omega$ , 2 W, Fusible/Flame Proof Wire Wound                                                | Vitrohm                                        | CRF253-4 10R                        |

| 23   | 1   | T1                   | Custom Transformer, EE16, 10pins; per<br>Power Integrations' RD-158 Transformer<br>Specification | Santronics<br>Ice Components<br>Precision, Inc | SNXR1346<br>TP07161<br>019-6120-00R |

| 24   | 1   | U1                   | LinkSwitch-II, LNK616PG, CV/CC, DIP-8C                                                           | Power<br>Integrations                          | LNK616PG                            |

| 25   | 1   | J3                   | Plastic housing for cable assembly                                                               | JST Sales<br>America Inc.                      | HER-2                               |

# 7 Transformer Specification

# 7.1 Electrical Diagram

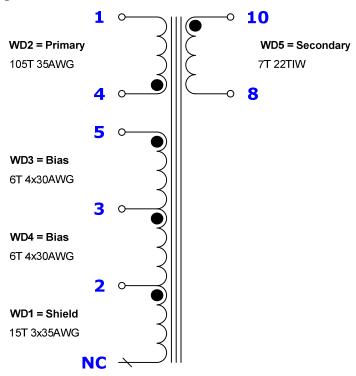

Figure 4 – Transformer Electrical Diagram.

# 7.2 Electrical Specifications

| Electrical Strength        | trical Strength 60 seconds, 60 Hz, from Pins 1-5 to Pins 6-10                |                |  |  |

|----------------------------|------------------------------------------------------------------------------|----------------|--|--|

| Primary Inductance         | Pins 1-4, all other windings open, measured at 100 kHz, 0.4 $V_{\text{RMS}}$ | 1.074 mH, ±10% |  |  |

| Resonant Frequency         | Pins 1-4, all other windings open                                            | 1000 kHz (min) |  |  |

| Primary Leakage Inductance | Pins 1-4, with Pins 8-10 shorted, measured at 100 kHz, 0.4 $V_{\text{RMS}}$  | 95 μH (max)    |  |  |

#### 7.3 Materials

| Item | Description                                                                |

|------|----------------------------------------------------------------------------|

| [1]  | Core: EE16, NC-2H or equivalent, gapped for ALG of 88.55 nH/T <sup>2</sup> |

| [2]  | Bobbin: EE16, Horizontal, 10 pins, (5/5). See attached drawing             |

| [3]  | Magnet Wire: #35 AWG, for the Shield and the Primary Winding               |

| [4]  | Magnet Wire: #30 AWG, for the Bias Winding                                 |

| [5]  | Triple Insulated Wire: #22 AWG, for the Secondary Winding                  |

| [6]  | Margin tape: 1.0 mm wide                                                   |

| [7]  | Tape: 3M 1298 Polyester film, 2.0 mils thick, 8.0 mm wide                  |

| [8]  | Tape: 3M Polyester film, 2.0 mils thick, 7.0 mm wide                       |

| [9]  | Varnish                                                                    |

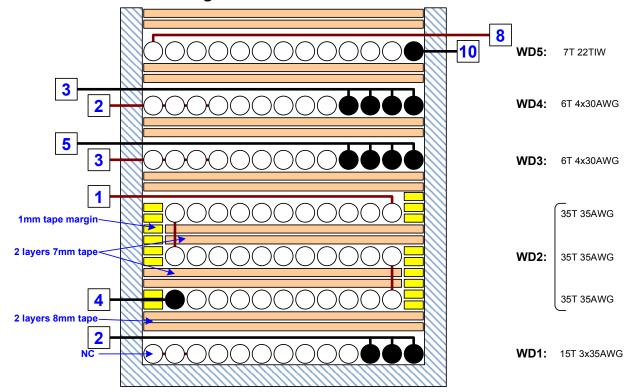

# 7.4 Transformer Build Diagram

Figure 5 - Transformer Build Diagram.

The highlighted 1 mm tape margin (in yellow above) was added to improve consistency in EMI performance in production. The spacing of the first two layers of the primary winding improves the effect of the subsequent shield windings and makes the transformer design less sensitive to winding variations. However, if the transformer can be manufactured consistently to comply with EMI performance specifications without the extra margin tape, omit the margin tape to reduce transformer cost and increase the wire gauge of the primary winding so that each layer fills the bobbin window width in 35 turns.

# 7.5 Transformer Construction

| Bobbin Preparation               | Primary side of the bobbin is placed on the left hand side, and secondary side of the bobbin is placed on the right hand side.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| WD1<br>Shield                    | Temporarily hang the start end of the wires of item [3] on pin 7, wind 15 tri-filar turns from right to left with tight tension and evenly. The maximum allowed gap between the winding and the left and right lateral walls of the bobbin must be less than 0.5 mm (20 mils). Cut the end of the wire and bring the start end of the wire across the bobbin to the left to terminate at pin 2.                                                                                                                                                                                                                                                |  |  |  |  |  |

| Insulation                       | 2 layers of tape item [7].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| WD2<br>Primary                   | Apply 1 mm margin tape on both side of bobbin to match the height of one layer of primary winding on the left side, and two layers of primary winding on the right side. Start at pin 4, wind 35 turns of item [3] from left to right with tight tension, and apply 2 layers tape item [8] and 1 mm margin tape to match another two layers of primary on the left side. Continue winding 35 turns of item [3] from right to left, repeat 2 layers tape item [8] and 1 mm margin tape on the left side, continue wind another 35 turns of item [3] from left to right, at the last turn bring the wire back to the left to terminate at pin 1. |  |  |  |  |  |

| Insulation                       | 2 layers of tape item [7].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| WD3<br>1 <sup>st</sup> half Bias | Temporarily hang the start end of the wires on pin 6, wind 6 quad-filar turns of item [4] from right to left uniformly, terminate the end of the wires at pin 3, bring the start end of the wires across the bobbin to the left side to terminate at pin 5.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Insulation                       | 2 layers of tape item [7].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| WD4<br>2 <sup>nd</sup> half Bias | Temporarily hang the start end of the wires of item [4] on pin 6, wind 6 quad-filar turns of item [4] from right to left uniformly, terminate the end of the wires at pin 2, bring the start end of the wires across the bobbin to the left side to terminate at pin 3.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Insulation                       | 2 layers of tape item [7].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| WD5<br>Secondary                 | Start pin 10, wind 7 turns of item [5] from right to left uniformly, at the last turn bring the wire across the bobbin to the right side to terminate at pin 8. Cut three pins from the secondary side: 6, 7, and 9.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Insulation                       | 2 layers of tape item [7].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| Finish                           | Grind the core to get 1.074mH. Secure the core with tape. Dip vanish [9].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| L                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

### Note:

1. Tape between adjacent primary winding layers reduces primary capacitance and losses.

# 8 Design Spreadsheet

| RD-158 Power<br>Integrations | INPUT             | INFO | OUTPUT | UNIT | ACDC_LinkSwitch-II_040108_Rev1-0.xls;<br>LinkSwitch-II Discontinuous Flyback<br>Transformer Design Spreadsheet |

|------------------------------|-------------------|------|--------|------|----------------------------------------------------------------------------------------------------------------|

| ENTER APPLICAT               | <b>TION VARIA</b> | BLES |        |      |                                                                                                                |

| VACMIN                       | 85                |      |        | V    | Minimum AC Input Voltage                                                                                       |

| VACMAX                       | 265               |      |        | V    | Maximum AC Input Voltage                                                                                       |

| fL                           | 50                |      |        | Hz   | AC Mains Frequency                                                                                             |

| VO                           | 5                 |      |        | V    | Output Voltage (at continuous power)                                                                           |

| 10                           | 1                 |      |        | Α    | Power Supply Output Current                                                                                    |

|                              |                   |      |        |      | (corresponding to peak power)                                                                                  |

| Power                        |                   |      | 5.00   | W    | Continuous Output Power                                                                                        |

| n                            |                   |      | 0.70   |      | Efficiency Estimate at output terminals.                                                                       |

|                              |                   |      |        |      | Under 0.7 if no better data available                                                                          |

| Z                            |                   |      | 0.50   |      | Z Factor. Ratio of secondary side losses to                                                                    |

|                              |                   |      |        |      | the total losses in the power supply. Use 0.5                                                                  |

|                              |                   |      |        |      | if no better data available                                                                                    |

| tC                           |                   |      | 3.00   | ms   | Bridge Rectifier Conduction Time Estimate                                                                      |

| Add Bias Winding             | YES               |      | YES    |      | Choose Yes to add a Bias winding to power                                                                      |

|                              |                   |      |        |      | the LinkSwitch-II.                                                                                             |

| CIN                          | 14.7              |      |        | uF   | Input Capacitance                                                                                              |

| ENTER LinkSwitc | h-II VARIABI | LES    |     |                                                       |

|-----------------|--------------|--------|-----|-------------------------------------------------------|

| Chosen Device   | LNK616       | LNK616 |     | Chosen LinkSwitch-II device                           |

| Package         | PG           | PG     |     | Select package (PG, GG or DG)                         |

| ILIMITMIN       |              | 0.39   | Α   | Minimum Current Limit                                 |

| ILIMITTYP       |              | 0.41   | Α   | Typical Current Limit                                 |

| ILIMITMAX       |              | 0.45   | Α   | Maximum Current Limit                                 |

| FS              | 67.25        | 67.25  | kHz | Typical Device Switching Frequency at                 |

|                 |              |        |     | maximum power                                         |

| VOR             |              | 82.50  | V   | Reflected Output Voltage (VOR < 135 V<br>Recommended) |

| VDS             |              | 10.00  | V   | LinkSwitch-II on-state Drain to Source<br>Voltage     |

| VD              |              | 0.50   | V   | Output Winding Diode Forward Voltage                  |

| 1/5             |              | 2.24   |     | Drop                                                  |

| KP              |              | 2.31   |     | Ensure KDP > 1.3 for discontinuous mode operation     |

| FEEDBACK WINDING PARAMET | ERS  |   |                        |  |

|--------------------------|------|---|------------------------|--|

| NFB                      | 6.00 |   | Feedback winding turns |  |

| VFLY                     | 4.71 | V | Flyback Voltage        |  |

| VFOR                     | 5.00 | V | Forward voltage        |  |

| BIAS WINDING P | ARAMETERS |      |   |                                         |

|----------------|-----------|------|---|-----------------------------------------|

| VB             | 9         | 9.00 | V | Bias Winding Voltage. Ensure that VB >  |

|                |           |      |   | VFLY. Bias winding is assumed to be AC- |

|                |           |      |   | STACKED on top of Feedback winding      |

| NB             |           | 6.00 |   | Bias Winding number of turns            |

|                |           |      |   |                                         |

| DESIGN PARAMI | ETERS |       |       |                                                          |

|---------------|-------|-------|-------|----------------------------------------------------------|

| DCON          | 4.5   | 4.50  | us    | Output diode conduction time                             |

| TON           |       | 4.31  | us    | LinkSwitch-II On-time (calculated at minimum inductance) |

| RUPPER        |       | 12.88 | k-ohm | Upper resistor in Feedback resistor divider              |

| RLOWER        |       | 9.16  | k-ohm | Lower resistor in resistor divider                       |

| ENTER TRANSFORMER CORE/CONSTRUCTION VARIABLES |      |             |               |                                                                                               |

|-----------------------------------------------|------|-------------|---------------|-----------------------------------------------------------------------------------------------|

| Core Type                                     |      |             |               |                                                                                               |

| Core                                          | EE16 | EE16        |               | Enter Transformer Core. Based on the output power the recommended core sizes are EE19 or EE22 |

| Bobbin                                        |      | EE16 BOBBIN |               | Generic EE16_BOBBIN                                                                           |

| AE                                            |      | 19.20       | mm^2          | Core Effective Cross Sectional Area                                                           |

| LE                                            |      | 35.00       | mm^2          | Core Effective Path Length                                                                    |

| AL                                            |      | 1140.00     | nH/turn<br>^2 | Ungapped Core Effective Inductance                                                            |

| BW                                            |      | 8.60        | mm            | Bobbin Physical Winding Width                                                                 |

| М                                             |      | 0.00        | mm            | Safety Margin Width (Half the Primary to Secondary Creepage Distance)                         |

| L                                             |      | 3.00        |               | Number of Primary Layers                                                                      |

| NS                                            |      | 7.00        |               | Number of Secondary Turns. To adjust<br>Secondary number of turns change DCON                 |

| DC INPUT VOLTAGE PARAMETERS |       |     |                        |  |

|-----------------------------|-------|-----|------------------------|--|

| VMIN                        | 87.45 | 5 V | Minimum DC bus voltage |  |

| VMAX                        | 374.7 | 7 V | Maximum DC bus voltage |  |

| CURRENT WAVEFORM SHAPE PARAMETERS |      |   |                                     |  |

|-----------------------------------|------|---|-------------------------------------|--|

| DMAX                              | 0.29 |   | Maximum duty cycle measured at VMIN |  |

| IAVG                              | 0.09 | Α | Input Average current               |  |

| IP                                | 0.39 | Α | Peak primary current                |  |

| IR                                | 0.39 | Α | primary ripple current              |  |

| IRMS                              | 0.14 | Α | Primary RMS current                 |  |

| TRANSFORMER PRIMARY DESIGN | PARAMETE | RS            |                                             |

|----------------------------|----------|---------------|---------------------------------------------|

| LPMIN                      | 966.73   | uН            | Minimum Primary Inductance                  |

| LPTYP                      | 1074.14  | uН            | Typical Primary inductance                  |

| LP_TOLERANCE               | 10.00    |               | Tolerance in primary inductance             |

| NP                         | 105.00   |               | Primary number of turns. To adjust Primary  |

| 41.0                       | 07.00    | -1.1/1        | number of turns change BM_TARGET            |

| ALG                        | 87.68    | nH/turn<br>^2 | Gapped Core Effective Inductance            |

| BM_TARGET 2200             | 2200.00  | Gauss         | Target Flux Density                         |

| BM                         | 2184.51  | Gauss         | Maximum Operating Flux Density              |

|                            |          |               | (calculated at nominal inductance), BM <    |

|                            |          |               | 2500 is recommended                         |

| BP                         | 2643.26  | Gauss         | Peak Operating Flux Density (calculated at  |

|                            |          |               | maximum inductance and max current limit),  |

|                            |          |               | BP < 3000 is recommended                    |

| BAC                        | 1092.26  | Gauss         | AC Flux Density for Core Loss Curves (0.5   |

|                            |          |               | X Peak to Peak)                             |

| ur                         | 165.37   |               | Relative Permeability of Ungapped Core      |

| LG                         | 0.25     | mm            | Gap Length (LG > 0.1 mm)                    |

| BWE                        | 25.80    | mm            | Effective Bobbin Width                      |

| OD                         | 0.25     | mm            | Maximum Primary Wire Diameter including     |

|                            |          |               | insulation                                  |

| INS                        | 0.05     |               | Estimated Total Insulation Thickness (= 2 * |

|                            |          |               | film thickness)                             |

| DIA                        | 0.20     | mm            | Bare conductor diameter                     |

| AWG                        | 33.00    |               | Primary Wire Gauge (Rounded to next         |

|                            |          |               | smaller standard AWG value)                 |

| CM                         | 50.80    |               | Bare conductor effective area in circular   |

| CNAA                       | 000.50   |               | mils                                        |

| CMA                        | 362.53   |               | Primary Winding Current Capacity (200 <     |

|                            |          |               | CMA < 500)                                  |

| TRANSFORMER SECONDARY DESIGN PARAMETERS |        |   |                                                                     |

|-----------------------------------------|--------|---|---------------------------------------------------------------------|

| Lumped parameters                       |        |   |                                                                     |

| ISP                                     | 5.84   | Α | Peak Secondary Current                                              |

| ISRMS                                   | 2.16   | Α | Secondary RMS Current                                               |

| IRIPPLE                                 | 1.92   | Α | Output Capacitor RMS Ripple Current                                 |

| CMS                                     | 432.77 |   | Secondary Bare Conductor minimum circular mils                      |

| AWGS                                    | 23.00  |   | Secondary Wire Gauge (Rounded up to next larger standard AWG value) |

| VOLTAGE STRESS PARAMETERS |        |   |                                                                                                                |

|---------------------------|--------|---|----------------------------------------------------------------------------------------------------------------|

| VDRAIN                    | 568.02 | V | Maximum Drain Voltage Estimate (Assumes 20% Zener clamp tolerance and an additional 10% temperature tolerance) |

| PIVS                      | 29.98  | V | Output Rectifier Maximum Peak Inverse Voltage                                                                  |

Note: Different spreadsheet revisions may give slightly different spreadsheet values.

### 9 Performance Data

All measurements were taken at room temperature unless otherwise specified, with 60 Hz input frequency. Measurements were taken at the end of a 6 ft, 0.3  $\Omega$ , 24 AWG output cable.

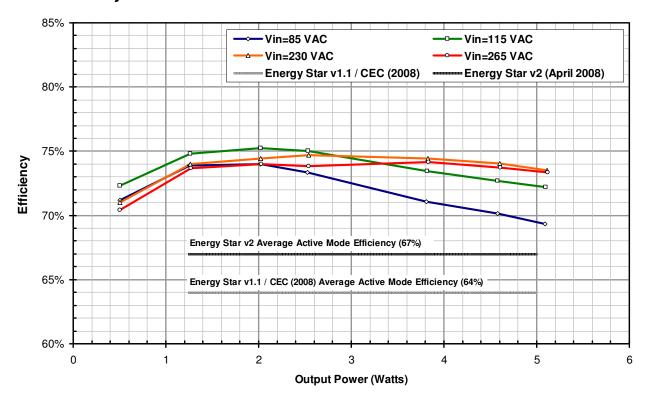

# 9.1 Efficiency

Figure 6 - Efficiency vs. Output Power.

#### 9.2 Active Mode CEC Measurement Data

The power supply passes both Energy Star v1.1 and v2 (April 2008) limits.

| % of Full Load   | Efficiency (%) |         |  |  |

|------------------|----------------|---------|--|--|

| 70 01 1 dii 20dd | 115 VAC        | 230 VAC |  |  |

| 25               | 74.8           | 74.0    |  |  |

| 50               | 75.0           | 74.7    |  |  |

| 75               | 73.5           | 74.4    |  |  |

| 100              | 72.2           | 73.5    |  |  |

| Average          | 73.9%          | 74.2%   |  |  |

| Energy Star v1.1 | 64%            | 64%     |  |  |

| Energy Star v2   | 67%            | 67%     |  |  |

Figure 7 – Average Active Mode Efficiency.

### 9.2.1 Energy Star v1.1 / CEC (2008)

As part of the U. S. Energy Independence and Security Act of 2007 all single-output adapters, including those provided with products for sale in the USA after July 1, 2008, must meet the Energy Star v1.1 specification for minimum active-mode efficiency and noload input power. Note that battery chargers are exempt from these requirements except in the state of California, where they must also be compliant.

Minimum active-mode efficiency is defined as the average efficiency at 25%, 50%, 75%, and 100% of rated output power with the limit based on the nameplate output power:

| Nameplate Output (P <sub>NP</sub> ) | Minimum Efficiency in Active Mode of Operation      |

|-------------------------------------|-----------------------------------------------------|

| < 1 W                               | $0.5 \times P_{NP}$                                 |

| ≥ 1 W to ≤ 49 W                     | $0.09 \times \ln (P_{NP}) + 0.5$ [In = natural log] |

| > 49 W                              | 0.84                                                |

| Nameplate Output (P <sub>NP</sub> ) | Maximum No-load Input Power |

|-------------------------------------|-----------------------------|

| All                                 | ≤ 0.5 W                     |

For single-input voltage adapters the measurement is made at the rated (single) nominal input voltage only (either 115 VAC or 230 VAC). For universal input adapters, the measurement is made at both nominal input voltages (115 VAC and 230 VAC).

To meet the standard, the measured average efficiency (or efficiencies for universal input supplies) must be greater than or equal to the efficiency specified by the CEC/Energy Star v1.1 standard.

# 9.2.2 Energy Star v2 (April 2008)

The Energy Star v2 specification (planned to take effect Nov 1, 2008) increases the previously stated requirements.

### Standard Models

| Nameplate Output (P <sub>NP</sub> ) | Minimum Efficiency in Active Mode of Operation (Rounded to Hundreds) |

|-------------------------------------|----------------------------------------------------------------------|

| ≤ 1 W                               | $\geq 0.48 \times P_{NP} + 0.14$                                     |

| > 1 W to ≤ 49 W                     | $\geq 0.0626 \times \ln (P_{NP}) + 0.622$<br>[In = natural log]      |

| > 49 W                              | 0.87                                                                 |

| Nameplate Output (P <sub>NP</sub> ) | Maximum No-load Input Power |

|-------------------------------------|-----------------------------|

| 0 to <50 W                          | ≤ 0.3 W                     |

| ≥50 to ≤250 W                       | ≤ 0.5 W                     |

### Low-voltage Models

A low-voltage model is an external power supply (EPS) with a nameplate output voltage of less than 6 V and a nameplate output current greater than or equal to 550 mA.

| Nameplate Output (P <sub>NP</sub> ) | Minimum Efficiency in Active Mode of Operation (Rounded to Hundreds) |

|-------------------------------------|----------------------------------------------------------------------|

| ≤1 W                                | $\geq 0.497 \times P_{NP} + 0.067$                                   |

| >1 W to ≤49 W                       | $\geq 0.075 \times \ln (P_{NP}) + 0.561$ [In = natural log]          |

| >49 W                               | ≥ 0.86                                                               |

| Nameplate Output (P <sub>NP</sub> ) | Maximum No-load Input Power |  |

|-------------------------------------|-----------------------------|--|

| 0 to <50 W                          | ≤ 0.3 W                     |  |

| ≥50 to ≤250 W                       | ≤ 0.5 W                     |  |

For the latest up-to-date information, please visit the PI Green Room at <u>www.powerint.com</u>.

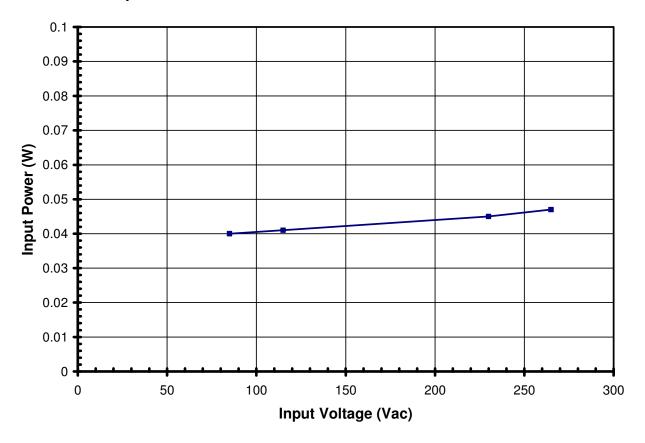

# 9.3 No-Load Input Power

Figure 8 - Zero Load Input Power vs. Input Line Voltage, Room Temperature, 60 Hz. (To achieve no-load of less than 30 mW, remove the preload resistor (R9) and replace it with a 6.2 V clamp diode).

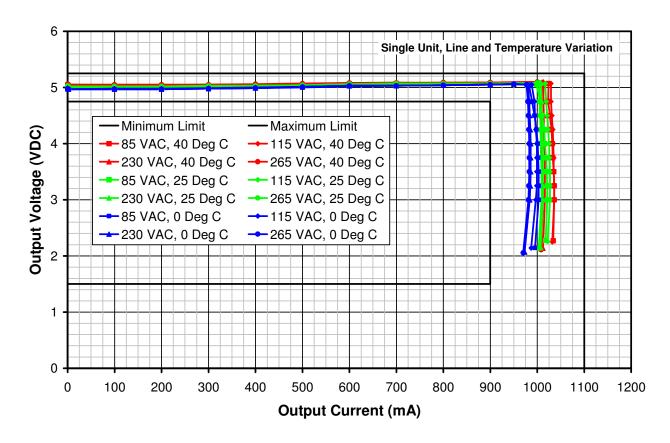

#### 9.4 Regulation

#### 9.4.1 Load, Line and Temperature

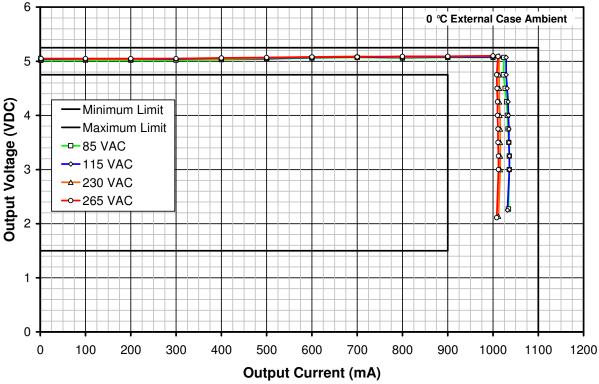

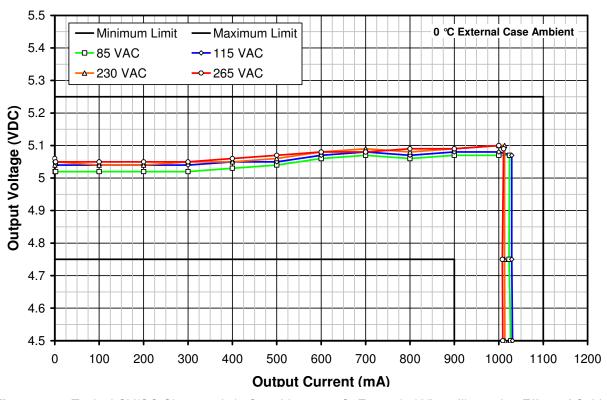

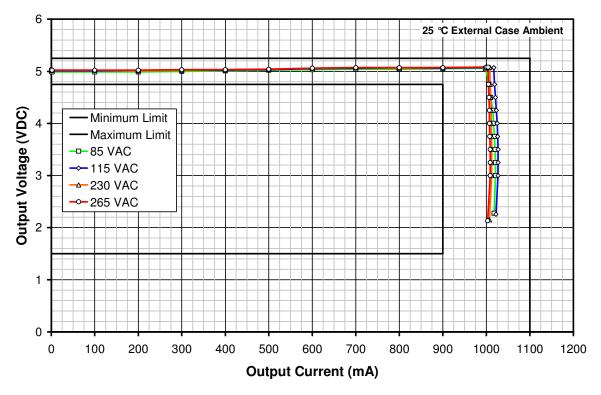

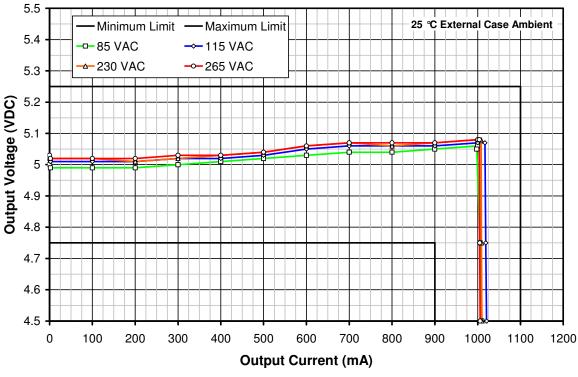

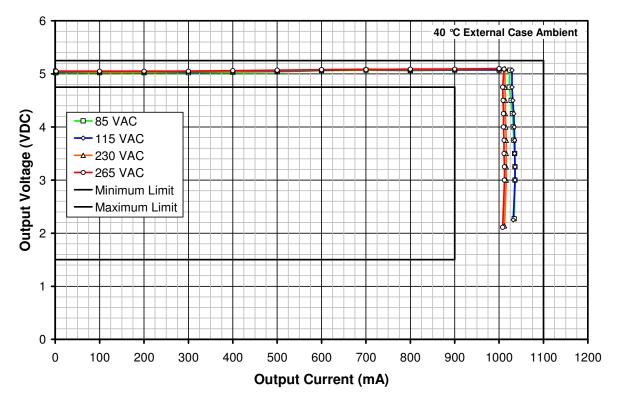

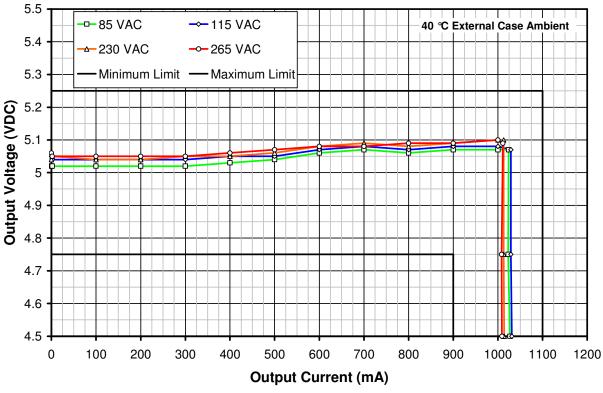

The output characteristic was tested at the end of a 6' output cable. The DC resistance of the cable was approximately 0.3  $\Omega$ .

The measurements were made with the supply inside a sealed plastic enclosure which was then placed within a cardboard box. The cardboard box ensures air flow from the thermal chamber does not affect the test. The ambient temperature inside the cardboard box was monitored, and the temperature of the thermal chamber was adjusted to maintain the desired temperature.

The unit was allowed to thermally stabilize for 30 minutes, unloaded, at each measurement temperature prior to data being recorded.

Figure 9 - Composite Output Regulation Across Load, Line, and Temperature.

Figure 10 − Typical CV/CC Characteristic Over Line at 0 °C.

Figure 11 - Typical CV/CC Characteristic Over Line at 0 °C. Expanded View, Illustrating Effect of Cable Drop Compensation.

Figure 12 - Typical CV/CC Characteristic Over Line at 25 °C.

**Figure 13** – Typical CV/CC Characteristic Over Line at 25 °C. Expanded View Illustrating Effect of Cable Drop Compensation.

Figure 14 – Typical CV/CC Characteristic Over Line at 40 °C.

Figure 15 - Typical CV/CC Characteristic Over Line at 40 °C. Expanded View Illustrating Effect of Cable Drop Compensation.

# 10 Thermal Performance

# 10.1 Operating Temperature Survey

Thermal performance was measured inside an enclosure at full load with no airflow. A thermocouple was attached to U1's source pin.

| Item          | 85 VAC | 115 VAC | 175 VAC | 230 VAC | 265 VAC |

|---------------|--------|---------|---------|---------|---------|

| Ambient       | 40 °C  | 40 °C   | 40 °C   | 40 °C   | 40 °C   |

| U1 Source Pin | 97 °C  | 90.7 °C | 89.3 °C | 90.6 °C | 93.1 °C |

## 11 Waveforms

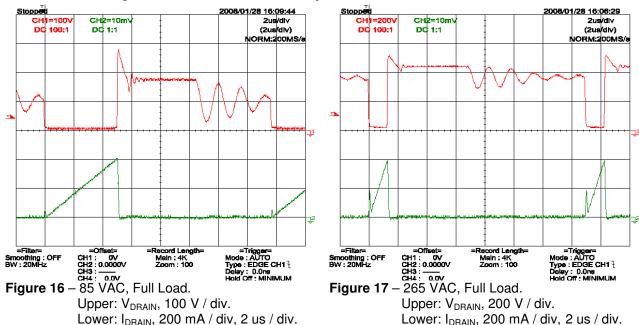

## 11.1 Drain Voltage and Current, Normal Operation

# 11.2 Output Voltage Start-up Profile

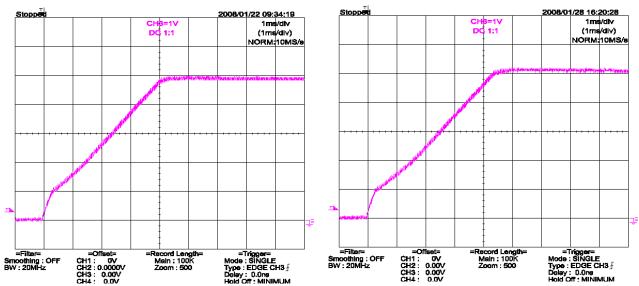

## 11.2.1 No-Load Output Voltage Start-up Characteristic

Figure 18 – Start-up Profile (No Load), 115 VAC, 1 V, 1 ms / div.

Figure 19 – Start-up Profile (No Load), 230 VAC, 1 V, 1 ms / div.

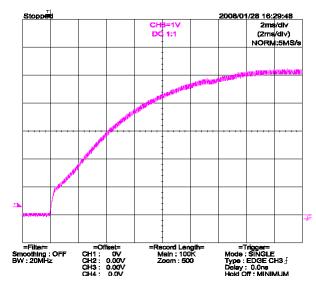

# 11.2.2 Output Voltage Start-up Characteristic - Resistive Load (5 $\Omega$ )

The voltage was measured at the load.

Figure 20 – Start-up Profile, 115 VAC, 1 V, 2 ms / div.

Figure 21 – Start-up Profile, 230 VAC, 1 V, 2 ms / div.

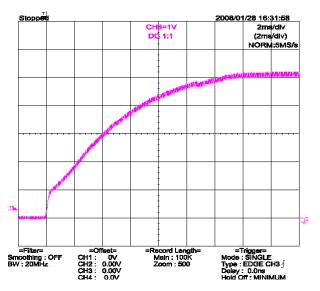

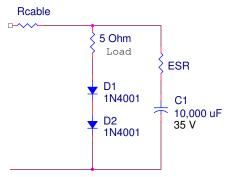

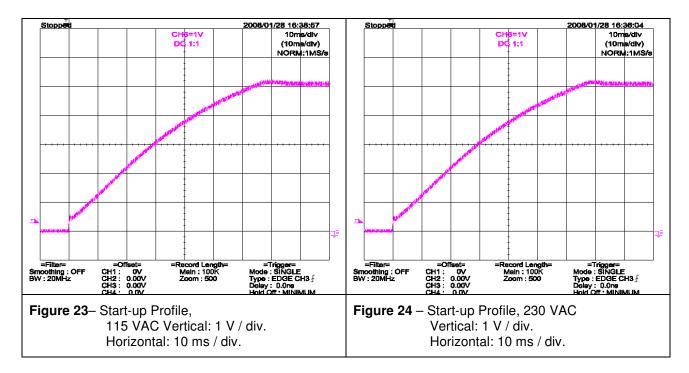

# 11.2.3 Output Voltage Start-up Characteristic - Battery-simulator Load

Figure 22 – Battery Simulator Schematic.

The voltage was measured at the PCB.

# 11.3 Drain Voltage and Current Start-up Profile

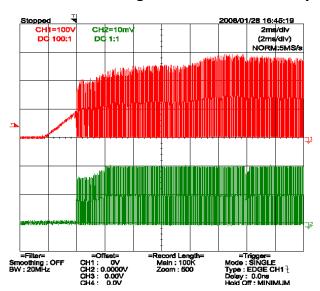

Figure 25 – 85 VAC Input and Maximum Load Upper V<sub>DRAIN</sub>, 100 V, 2 ms / div. Lower: I<sub>DRAIN</sub>, 200 mA / div.

Figure 26 – 265 VAC Input and Maximum Load Upper: V<sub>DRAIN</sub>, 200 V, 2 ms / div. Lower: I<sub>DRAIN</sub>, 200 mA / div.

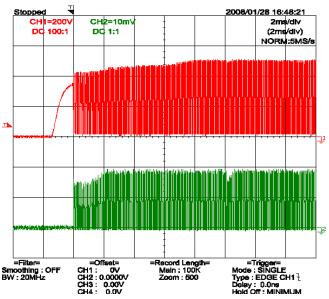

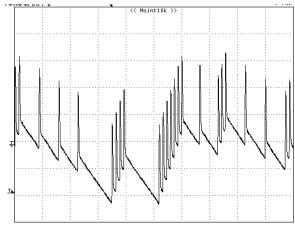

# 11.4 Load Transient Response (50% to 100% Load Step)

Figure 27 - Transient Response, 115 VAC 100-50-100% Load Step Output Voltage 100 mV, 5 ms / div.

Figure 28 - Transient Response, 230 VAC 100-50-100% Load Step Output Voltage 100 mV, 5 ms / div.

#### 11.5 Output Ripple Measurements

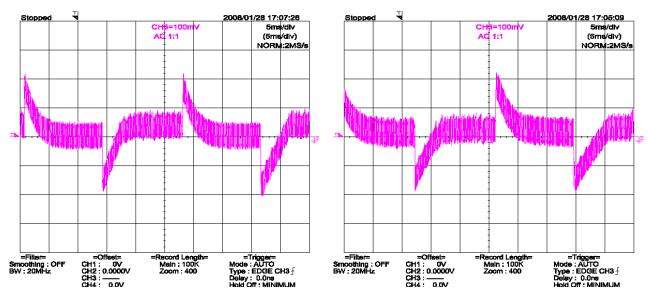

### 11.5.1 Ripple Measurement Technique

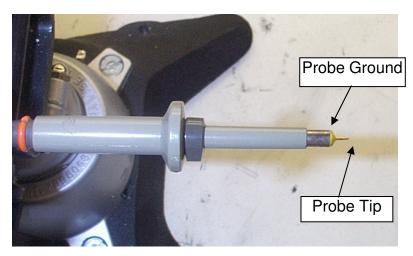

For DC output ripple measurements, use a modified oscilloscope test probe to reduce spurious signals. Details of the probe modification are provided in figures below.

Tie two capacitors in parallel across the probe tip of the 4987BA probe adapter. Use a 0.1  $\mu$ F / 50 V ceramic capacitor and 1.0  $\mu$ F / 50 V aluminum electrolytic capacitor. The aluminum-electrolytic capacitor is polarized, so always maintain proper polarity across DC outputs.

Figure 29 - Oscilloscope Probe Prepared for Ripple Measurement (End Cap and Ground Lead Removed).

**Figure 30** – Oscilloscope Probe with Probe Master 4987BA BNC Adapter (Modified with Wires for Probe Ground for Ripple measurement and Two Parallel Decoupling Capacitors Added).

# 11.5.2 Ripple Measurement Results

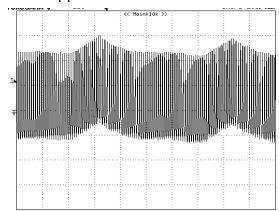

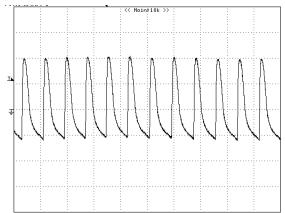

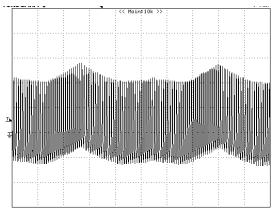

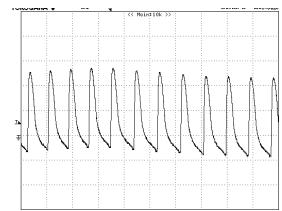

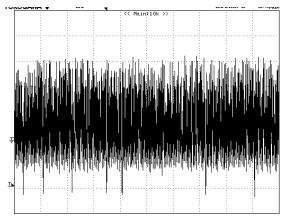

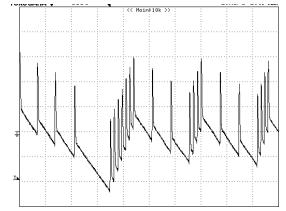

Figure 31 - Ripple, 85 VAC, Full Load, 20 mV, 200 V / div.

Figure 32 - Ripple, 85 VAC, Full Load, 20 mV,  $20 \mu \text{s}$  / div.

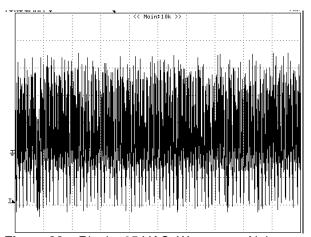

Figure 33 - Ripple, 85 VAC, Worst-case Noise, 20 mV, 5 ms / div.

Figure 34 - Ripple, 85 VAC, Worst-case Noise, 20 mV, 100 Cs / div.

Figure 35 – Ripple, 265 VAC, Full Load, 20 mV, 200 µs / div.

**Figure 36** – Ripple, 265 VAC, Full Load, 20 mV, 20 μs / div.

Figure 37 – Ripple, 265 VAC, Worst Case Noise, 20 mV / div, 5 ms / div.

Figure 38 – Ripple, 265 VAC, Worst Case Noise, 20 mV / div, 100 μs / div.

# 12 Line Surge

Differential input line 1.2  $\mu s$  / 50  $\mu s$  surge testing to IEC61000-4-5 standards was completed on a single test unit. The input voltage was set at 230 VAC / 60 Hz. The output current was 1 A and operation was verified following each surge event.

| Surge<br>Level (V) | Input<br>Voltage<br>(VAC) | Injection<br>Location | Injection<br>Phase (°) | Test Result<br>(Pass/Fail) |

|--------------------|---------------------------|-----------------------|------------------------|----------------------------|

| +500               | 230                       | L to N                | 90                     | Pass                       |

| -500               | 230                       | L to N                | 90                     | Pass                       |

| +750               | 230                       | L to N                | 90                     | Pass                       |

| -750               | 230                       | L to N                | 90                     | Pass                       |

| +1000              | 230                       | L to N                | 90                     | Pass                       |

| -1000              | 230                       | L to N                | 90                     | Pass                       |

## 13 Conducted EMI

# 14 Revision History

| <b>Date</b><br>15-May-08<br>25-Nov-08 | Author<br>JAC<br>SF | <b>Revision</b> 1.0 1.0 | <b>Description and changes</b> Initial Release Updated no-load graph caption text in Figure 8 | <b>Reviewed</b><br>JD |

|---------------------------------------|---------------------|-------------------------|-----------------------------------------------------------------------------------------------|-----------------------|

|                                       |                     |                         |                                                                                               |                       |

# **Notes**

#### For the latest updates, visit our website: www.powerint.com

Power Integrations reserves the right to make changes to its products at any time to improve reliability or manufacturability. Power Integrations does not assume any liability arising from the use of any device or circuit described herein. POWER INTEGRATIONS MAKES NO WARRANTY HEREIN AND SPECIFICALLY DISCLAIMS ALL WARRANTIES INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT OF THIRD PARTY RIGHTS.

#### **PATENT INFORMATION**

The products and applications illustrated herein (including transformer construction and circuits external to the products) may be covered by one or more U.S. and foreign patents, or potentially by pending U.S. and foreign patent applications assigned to Power Integrations. A complete list of Power Integrations' patents may be found at www.powerint.com. Power Integrations grants its customers a license under certain patent rights as set forth at http://www.powerint.com/ip.htm.

The PI Logo, TOPSwitch, TinySwitch, LinkSwitch, DPA-Switch, PeakSwitch, EcoSmart, Clampless, E-Shield, Filterfuse, StackFET, PI Expert and PI FACTS are trademarks of Power Integrations, Inc. Other trademarks are property of their respective companies. ©Copyright 2008 Power Integrations, Inc.

#### **Power Integrations Worldwide Sales Support Locations**

#### WORLD HEADQUARTERS

5245 Hellyer Avenue San Jose, CA 95138, USA. Main: +1-408-414-9200 Customer Service: Phone: +1-408-414-9665 Fax: +1-408-414-9765

e-mail: usasales@powerint.com

#### **GERMANY**

Rueckertstrasse 3 D-80336, Munich Germany Phone: +49-89-5527-3911 Fax: +49-89-5527-3920 e-mail: eurosales@powerint.com

#### INDIA #1, 14th Main Road

Vasanthanagar Bangalore-560052 India Phone: +91-80-41138020 Fax: +91-80-41138023 e-mail: indiasales@powerint.com

#### **CHINA (SHENZHEN)**

**CHINA (SHANGHAI)**

Kerry Everbright City

Rm 1601/1610, Tower 1,

No. 218 Tianmu Road West,

Shanghai, P.R.C. 200070

Fax: +86-21-6354-6325

e-mail:

Phone: +86-21-6354-6323

chinasales@powerint.com

Rm A, B & C 4th Floor, Block C, Electronics Science and Technology Building, 2070 Shennan Zhong Rd, Shenzhen, Guangdong, China, 518031 Phone: +86-755-8379-3243 Fax: +86-755-8379-5828 e-mail:

chinasales@powerint.com

# **ITALY**

Via De Amicis 2 20091 Bresso MI - Italy Phone: +39-028-928-6000 Fax: +39-028-928-6009 e-mail: eurosales@powerint.com

#### **JAPAN**

Kosei Dai-3 Bldg., 2-12-11, Shin-Yokohama, Kohoku-ku, Yokohama-shi, Kanagawa 222-0033 Phone: +81-45-471-1021 Fax: +81-45-471-3717 e-mail:

japansales@powerint.com

#### **KOREA**

RM 602, 6FL Korea City Air Terminal B/D, Samsung-Dong, Kangnam-Gu, Seoul, 135-728, Korea Phone: +82-2-2016-6610 Fax: +82-2-2016-6630

e-mail: koreasales@powerint.com

### **SINGAPORE**

51 Newton Road. #15-08/10 Goldhill Plaza, Singapore, 308900 Phone: +65-6358-2160 Fax: +65-6358-2015

singaporesales@powerint.com

#### **TAIWAN**

5F, No. 318, Nei Hu Rd., Sec. 1 Nei Hu Dist. Taipei, Taiwan 114, R.O.C. Phone: +886-2-2659-4570 Fax: +886-2-2659-4550 e-mail:

taiwansales@powerint.com

#### UNITED KINGDOM

1st Floor, St. James's House East Street, Farnham Surrey, GU9 7TJ United Kingdom Phone: +44 (0) 1252-730-141 Fax: +44 (0) 1252-727-689 e-mail: eurosales@powerint.com

#### **APPLICATIONS HOTLINE** World Wide +1-408-414-9660

**APPLICATIONS FAX** World Wide +1-408-414-9760